**Pierre Schnarz**

## Security Patterns for AMP-based Embedded Systems

SSE-Dissertation 19

Software Systems Engineering

Institut für Informatik Lehrstuhl von Prof. Dr. Andreas Rausch

# Security Patterns for AMP-based Embedded Systems

### Doctoral Thesis (Dissertation)

to be awarded the degree of Doktor-Ingenieur (Dr. -Ing.)

> submitted by Pierre Schnarz from Alzenau

approved by the Department of Informatics, Clausthal University of Technology

## 2018

Dissertation Clausthal, SSE-Dissertation 19, 2018

Chairperson of the Board of Examiners Prof. Dr. Jörg P. Müller

Chief Reviewer Prof. Dr. Andreas Rausch

2. Reviewer Prof. Dr. Joachim Wietzke

3. Reviewer Prof. Dr. Jörn Eichler

Date of oral examination: December 19, 2018

Für Katrin

### Declaration

I hereby declare that except where specific reference is made to the work of others, the contents of this dissertation are original and have not been submitted in whole or in part for consideration for any other degree or qualification in this, or by any other university. This dissertation is my own work and contains nothing which is the outcome of work done in collaboration with others, except as specified in the text and Acknowledgements.

> Pierre Schnarz January 2019

### Acknowledgements - Danksagung

The probability that we may fail in the struggle ought not to deter us from the support of a cause we believe to be just.

Abraham Lincoln

Viele Menschen haben mich auf dem langen Weg bis zur Fertigstellung dieser Arbeit begleitet. Daher möchte ich mich hier bei all Jenen bedanken, die beigetragen haben mir dies zu ermöglichen.

Bei Prof. Dr. Joachim Wietzke bedanke ich mich für die Betreuung meiner Promotion. Gerade die Mitarbeit in seiner Forschungsgruppe und darüber hinaus hat mir die nötige Hartnäckigkeit vermittelt, welche es brauchte um dieses große Projekt zu Ende zu bringen.

Ich möchte mich außerdem bei Prof. Dr. Andreas Rausch bedanken, welcher mich in seinem Institut als Doktorand aufgenommen hat. Seine konstruktive Kritik und leitende Fragen haben mir geholfen den Inhalt dieser Arbeit zu sortieren.

Des weiteren, möchte ich Prof. Dr. Ingo Stengel und Prof. Dr. Ronald Moore danken, welche mich gerade in der Anfangsphase der Promotion begleitet haben.

Frau Prof. Dr. Elke Hergenröther und Herrn Prof. Dr. Urs Andelfinger bedanke ich mich für die Unterstützung seitens der Hochschule Darmstadt und die Chance meinen Weg über die TU Clausthal gehen zu können.

In der Zeit als wissenschaftlicher Mitarbeiter im In-Car Multimedia Labor haben mich meine Kollegen im Bereich der Technischen Informatik unterstützt. Daher möchte ich mich hier bei Bettina, Sergio, Michael, Manfred für die aufschlussreiche Zeit bedanken. Auch meine Doktorandenkollegen in unserer Forschungsgruppe trugen eine großen Teil dazu bei, diese Forschungsarbeit zu bestreiten. Hier möchte ich Clemens Fischer danken, welcher maßgeblich an der Umsetzung der Implementierungen beigetragen hat. Tobias Holstein für konstruktive Diskussionen rund um das Thema Multi-OS. Andreas Knirsch welcher mich zur Forschungsgruppe gebracht und in all den Jahren nicht nur bei Forschungsfragen zur Seite stand. Markus Glaab mit dem ich gerade in der zweiten Phase auch gerne über die fachlichen Themen hinaus philosophiert habe.

Gerade auch meine Arbeitskollegen welche ich außerhalb der Forschungsgruppe hatte und habe, ermutigten mich bei Zweifeln und unterstützten mich bei inhaltlichen Fragen.

Über alle Inhaltlichen Aspekte hinaus, ist es mein familiäres und soziales Umfeld welches dazu beigetragen hat mich vor allem als Mensch weiterzuentwickeln.

Meiner Familie danke ich für die Stütze in allen Lebenslagen. Gerade meine Eltern Ulrike und Reiner unterstützen mich vorbehaltlos bis zur Erreichung all meiner Ziele.

Meinen Freunden danke ich für das "Da" sein, um mir einen gewissen Abstand zur Arbeit zu ermöglichen. Sabine du bist ein Freund wie ihn sich jeder wünscht.

Außerordentlich möchte ich an dieser Stelle meiner Frau Katrin danken. Mit ihrer Nähe hat sie mich und unsere kleine Familie über all die Jahre getragen und stand über den Dingen. Der Erfolg dieses Projektes geht vor allem auf sie zurück. Ihr widme ich diese Arbeit.

### Abstract

The consolidation of diverse functionalities onto a single platform is an ongoing, and still emerging, trend in the development of automotive electronic control units. More and more, these software-intensive functions imply different requirements concerning their system quality. In the future, this so-called mixed-criticality systems will emerge and consolidate even more functions, towards large computational platforms. Through the advent of hardware virtualization features into automotive-grade microcontrollers, software partitioning on hardware-level has been made possible. Particularly, asynchronous multiprocessing (AMP) is suitable to host several domains "bare-metal" by utilising these hardware virtualization capabilities. The AMP paradigm aims to assign a group of hardware elements statically to a single software partition. This composition is referred to as asynchronous domain. AMP is considered to be very performance effective, while the effort of realising hypervisors is kept at a minimum. However, an important requirement of mixed-criticality systems is to provide a platform to consolidate functions with a high degree of freedom of interference, dependability and security. Particularly, the availability and integrity aspect of co-hosted functions need to be enforced. Notwithstanding the utilisation of a common hardware platform, side-effects might end up in severe vulnerabilities.

This work elaborates on security patterns considering the specific construction paradigm of AMP-based systems. The patterns include security problems and solutions describing the offensive and defensive aspects of the given context. A tailored security assessment methodology combines methods and tools to analyse, quantify and evaluate the particular artefacts. The vulnerability assessment conducted in this work revealed a surface for denial-of-service of shared last-level caches (LLC) and elevation-of-privilege and tampering threats by misusing co-processors. Accordingly, the exploitability of these threats is demonstrated by penetration tests. The strategy to solve these issues, a reordering of the system memory map is proposed. A domain-block based mapping is shown to partition the LLC, which limits in this way the interference of adjacent domains. Furthermore, memory-map shuffling is proposed, to limit the exploitability of elevation-of-privilege threats by obfuscating the target memory structure. The findings of the security problems are transferred into rules to detect the issues in system architecture models. Furthermore, it is proposed to implement on each system layer primary and secondary security countermeasures. Particularly, systems utilizing hardware protection capabilities this leads to a extensive defence-in-depth security architecture. Therefore, the concepts contribute to the deterrence and the prevention of adverse actions to physical memory.

### Table of contents

| Li       | List of figures x |         |                                              |     |

|----------|-------------------|---------|----------------------------------------------|-----|

| Li       | st of             | tables  |                                              | xix |

| 1        | Intr              | oducti  | ion                                          | 1   |

|          | 1.1               | Motiva  | ation of This Research                       | 2   |

|          | 1.2               | Resear  | rch Goal                                     | 5   |

|          | 1.3               | Struct  | ure                                          | 5   |

| <b>2</b> | Fun               | damer   | ntal Concepts                                | 9   |

|          | 2.1               | Profile | e of Asymmetric Multiprocessing Systems      | 10  |

|          |                   | 2.1.1   | Definitions and Terminology                  | 10  |

|          |                   | 2.1.2   | ToE Description                              | 13  |

|          |                   | 2.1.3   | Hardware Elements                            | 18  |

|          |                   | 2.1.4   | ToE MPSoC Components                         | 19  |

|          |                   | 2.1.5   | Security Problem Definition                  | 27  |

|          |                   | 2.1.6   | Security Objectives                          | 29  |

|          | 2.2               | Securi  | ty Engineering                               | 31  |

|          |                   | 2.2.1   | Introduction to Security Engineering         | 31  |

|          |                   | 2.2.2   | Security Assessment Methodology              | 49  |

|          | 2.3               | Resear  | rch Methodology                              | 54  |

|          | 2.4               | Summ    | ary                                          | 59  |

| 3        | Risł              | k Asse  | ssment: Driver Information System Case Study | 61  |

|          | 3.1               | ToE- a  | and Context Profiling                        | 62  |

| <br> |  |

|------|--|

|      |  |

|      |  |

|          |     | 3.1.1  | Mixed-Criticality Systems: A Case for AMP                                                                                                    |

|----------|-----|--------|----------------------------------------------------------------------------------------------------------------------------------------------|

|          |     | 3.1.2  | System Decomposition                                                                                                                         |

|          |     | 3.1.3  | Experimental Platform                                                                                                                        |

|          |     | 3.1.4  | Threat Context Analysis                                                                                                                      |

|          | 3.2 | Threa  | t and Attack Analysis 83                                                                                                                     |

|          |     | 3.2.1  | Threat Analysis                                                                                                                              |

|          |     | 3.2.2  | Attack Analysis                                                                                                                              |

|          | 3.3 | Risk A | Analysis                                                                                                                                     |

|          |     | 3.3.1  | Impact Analysis                                                                                                                              |

|          |     | 3.3.2  | Attack Potential Analysis                                                                                                                    |

|          |     | 3.3.3  | Risk Definition                                                                                                                              |

|          |     | 3.3.4  | Hypothesised Attacks                                                                                                                         |

|          | 3.4 | Summ   | nary                                                                                                                                         |

| 4        | Vul | nerabi | lity Assessment 97                                                                                                                           |

|          | 4.1 | Hyp-A  | Attack1: $PE_i$ disrupts $PE_j$ access to $LLC$                                                                                              |

|          |     | 4.1.1  | Vulnerability Analysis    99                                                                                                                 |

|          |     | 4.1.2  | Penetration Test: Cache Thrashing                                                                                                            |

|          | 4.2 | Hyp-A  | Attack2: $PE\sp{s}$ memory base is tampered with by adjacent $PE$ 120                                                                        |

|          |     | 4.2.1  | Vulnerability Analysis                                                                                                                       |

|          |     | 4.2.2  | Penetration Test: Co-Processor Exploit                                                                                                       |

|          | 4.3 | Gener  | alized Vulnerability and Exploitation Pattern                                                                                                |

|          |     | 4.3.1  | Modelling Protection Architectures                                                                                                           |

|          |     | 4.3.2  | Preliminaries of an AMP system                                                                                                               |

|          |     | 4.3.3  | Breach Access Controls on Intermediated Level                                                                                                |

|          |     | 4.3.4  | Denial-of-Service a Shared Resource                                                                                                          |

|          |     | 4.3.5  | Identification of Attack Surfaces in AMP Systems 136                                                                                         |

|          |     | 4.3.6  | Primary and Secondary Assets                                                                                                                 |

|          |     | 4.3.7  | Attack Objectives and Scenarios                                                                                                              |

|          | 4.4 | Summ   | nary                                                                                                                                         |

| <b>5</b> | Ris | k Trea | tment 145                                                                                                                                    |

|          | 5.1 | Risk 7 | $\Gamma reatment Strategy \dots \dots$ |

|          |     | 5.1.1  | Target and Residual Attack Potential                                                                                                         |

|          |     | 5.1.2  | Exploitation Prevention on the Intermediate Layer                                                                                            |

|          |     | 5.1.3  | Security Solution $\ldots \ldots 148$                           |

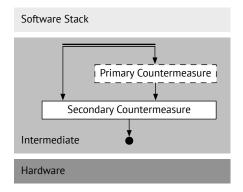

|          |     | 5.1.4  | Primary and Secondary Countermeasures                                                                                                        |

|   | 5.2            | Countermeasure 1: Memory Domain-Blocks                                                                                                                  | 54         |

|---|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

|   |                | 5.2.1 Effectiveness Requirements                                                                                                                        | 54         |

|   |                | 5.2.2 Mitigation Concept Analysis                                                                                                                       | 54         |

|   |                | 5.2.3 Proof-of-Concept Implementation                                                                                                                   | 57         |

|   | 5.3            | Countermeasure 2: Memory-Map Shuffling                                                                                                                  | 60         |

|   |                | 5.3.1 Effectiveness Requirements                                                                                                                        | 61         |

|   |                | 5.3.2 Mitigation Concept Analysis                                                                                                                       | 61         |

|   |                | 5.3.3 Case Study $\ldots \ldots \ldots$ | 68         |

|   | 5.4            | Summary                                                                                                                                                 | 70         |

| 6 | Sec            | urity Evaluation 17                                                                                                                                     | 73         |

|   | 6.1            | Domain-Block Memory Mapping                                                                                                                             | 74         |

|   |                | 6.1.1 Effectiveness Assessment                                                                                                                          | 74         |

|   |                | 6.1.2 Evaluation of the PoC Implementation                                                                                                              | 76         |

|   |                | 6.1.3 Residual Risk Analysis                                                                                                                            | 81         |

|   | 6.2            | Memory-Map Shuffling                                                                                                                                    | 33         |

|   |                | 6.2.1 Effectiveness Assessment                                                                                                                          | 33         |

|   |                | 6.2.2 Residual Risk Analysis                                                                                                                            | 36         |

|   | 6.3            | Comparison to Hypervisor-based System Architectures                                                                                                     | 38         |

|   |                | 6.3.1 Attack Potential: Cache-Thrashing                                                                                                                 | 39         |

|   |                | 6.3.2 Attack Potential: Tamper with Memory of Adjacent OS Guest . 19                                                                                    | 91         |

|   | 6.4            | Summary                                                                                                                                                 | 92         |

| 7 | $\mathbf{Rel}$ | ated Work 19                                                                                                                                            | <b>}</b> 5 |

|   | 7.1            | Security Requirements Engineering                                                                                                                       | 96         |

|   | 7.2            | Security Architectures of AMP-based Systems                                                                                                             | 98         |

|   | 7.3            | Offensive Methods and Attacks                                                                                                                           | 98         |

|   | 7.4            | Exploitation Prevention                                                                                                                                 | 00         |

|   | 7.5            | Summary                                                                                                                                                 | )2         |

| 8 | Cor            | nclusion 20                                                                                                                                             | )3         |

|   | 8.1            | Contents                                                                                                                                                | 04         |

|   | 8.2            | Contributions of this Research                                                                                                                          | 96         |

|   | 8.3            | Answers to the Research Questions                                                                                                                       | )8         |

|   |                | 8.3.1 Research Question 1 $\ldots \ldots 20$                                      | )8         |

|   |                | 8.3.2 Research Question 2                                                                                                                               | )9         |

|   | 8.4            | Limitations                                                                                                                                             | )9         |

|    |            | Future Work    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    .    . |     |  |  |  |

|----|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--|--|--|

| 9  | Acr        | onyms 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 213 |  |  |  |

| Re | References |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |  |  |  |

| A  | ppen       | dix A Technical Specification OMAP5 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 237 |  |  |  |

|    | A.1        | Schematics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 238 |  |  |  |

|    | A.2        | Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 239 |  |  |  |

## List of figures

| 2.1  | ToE overview.                                                         | 13 |

|------|-----------------------------------------------------------------------|----|

| 2.2  | Layered system hierarchy.                                             | 14 |

| 2.3  | Comparison of domain separation paradigms.                            | 18 |

| 2.4  | Considered Multiprocessor System-on-Chip (MPSoC) components           | 20 |

| 2.5  | Generalized MPSoCstructure combining diverse elements                 | 21 |

| 2.6  | Memory architecture                                                   | 22 |

| 2.7  | Communication architecture interface.                                 | 23 |

| 2.8  | System memory-map concept                                             | 26 |

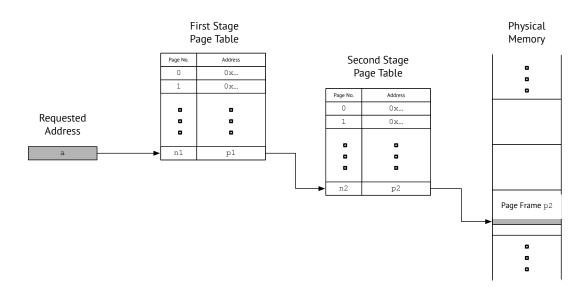

| 2.9  | Two-stage memory translation                                          | 26 |

| 2.10 | First and second page-table                                           | 27 |

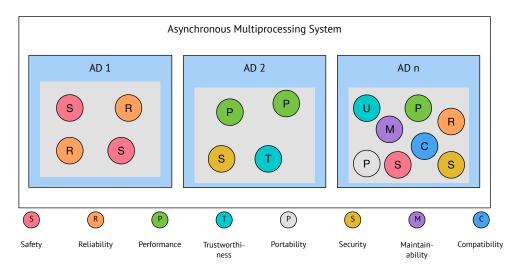

| 2.11 | System functions with a focus on particular product qualities         | 28 |

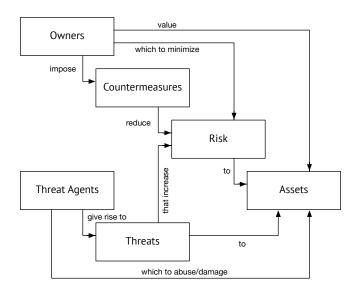

| 2.12 | The fundamental dependencies of actors and artefacts in security [41] | 32 |

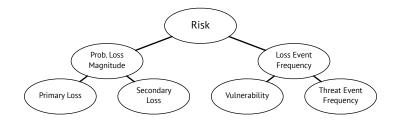

| 2.13 | FIRST ontology. (adopted from [49, p. 31])                            | 37 |

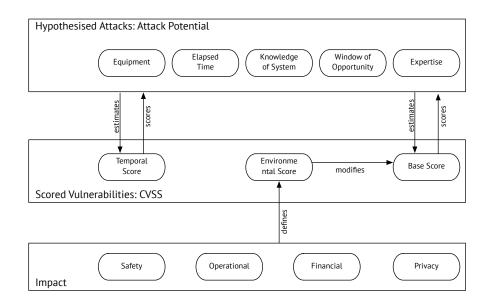

| 2.14 | Relationship of security metrics                                      | 49 |

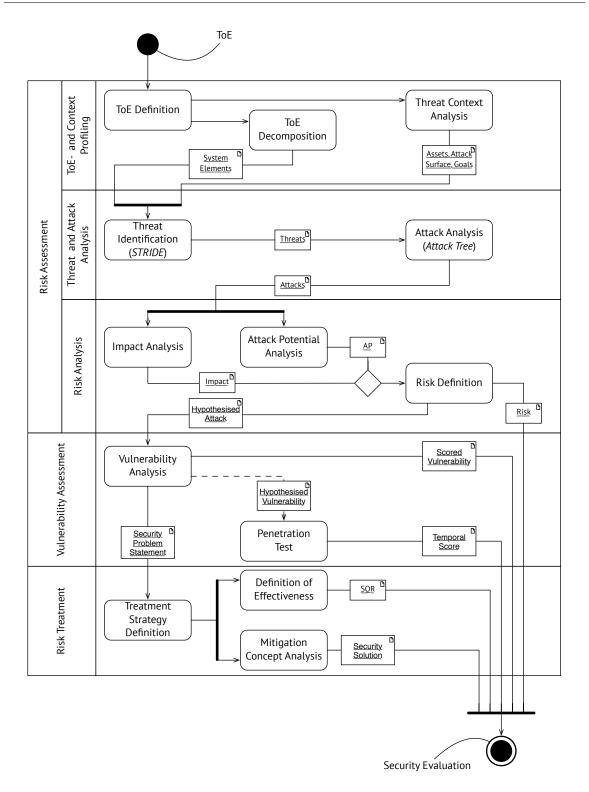

| 2.15 | Risk-based Security Assessment Process                                | 52 |

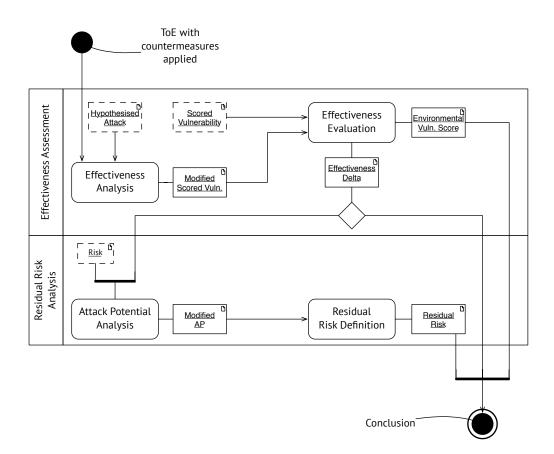

| 2.16 | Applied security evaluation process                                   | 53 |

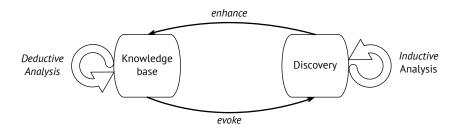

| 2.17 | Discovering security knowledge                                        | 54 |

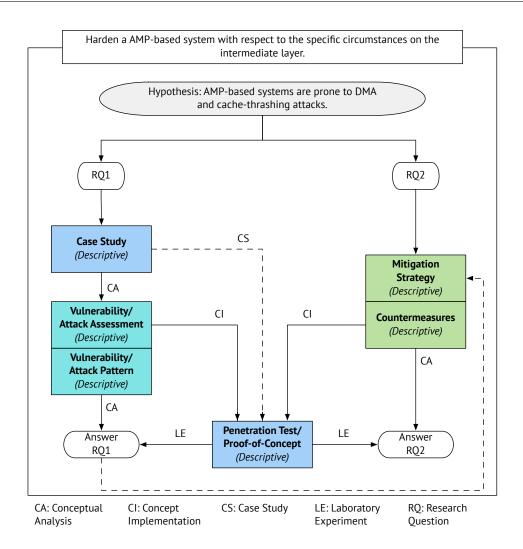

| 2.18 | Research Methodology                                                  | 55 |

| 3.1  | Quality assignment for the Driver Information System.                 | 64 |

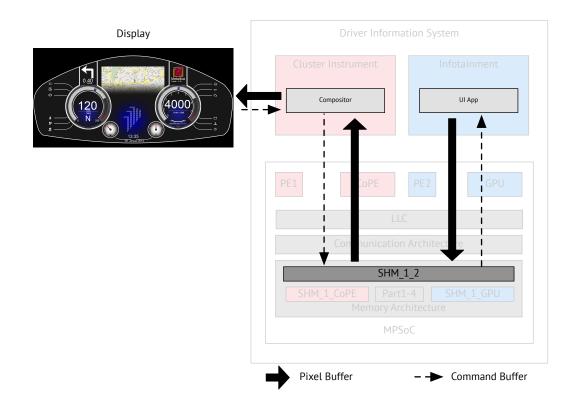

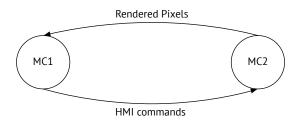

| 3.2  | Case Study: Driver Information System use case                        | 65 |

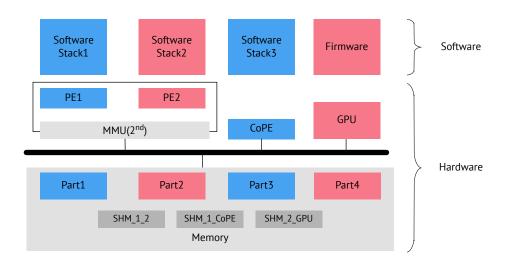

| 3.3  | Technical architecture and software stack assignments. $\ldots$       | 67 |

| 3.4  | Memory map overview.                                                  | 68 |

| 3.5  | Data flow diagram of the driver information system                    | 68 |

| 3.6  | Exemplary E/E architecture and functional domains                           | 69  |

|------|-----------------------------------------------------------------------------|-----|

| 3.7  | Texas Instruments OMAP5432 EVM [79]                                         | 70  |

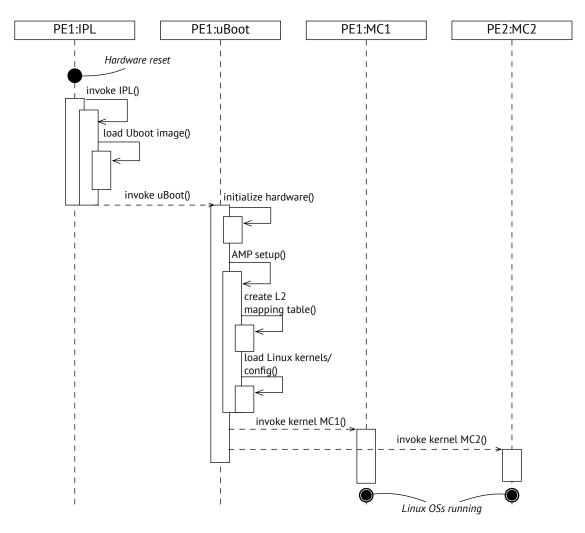

| 3.8  | Boot sequence of the experimental system setup                              | 74  |

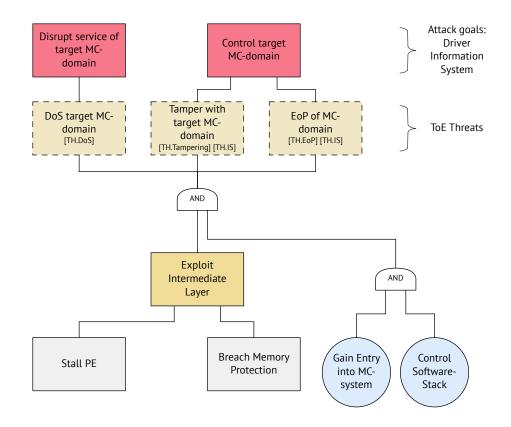

| 3.9  | Presumed path into the MC-system. To<br>E threats defined in 2.1.5          | 78  |

| 3.10 | Logical Level DFD                                                           | 84  |

| 3.11 | DFD of the technical platform. Dashed items are out-of-scope                | 87  |

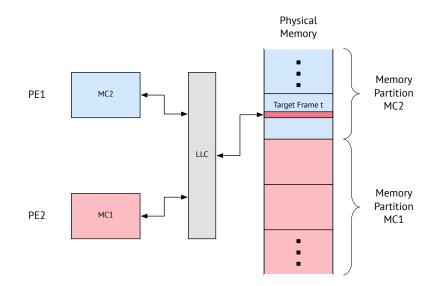

| 4.1  | Considered cache thrashing scenario.                                        |     |

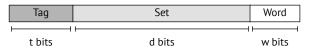

| 4.2  | Cache associativity mapping. [160, p. 132]                                  |     |

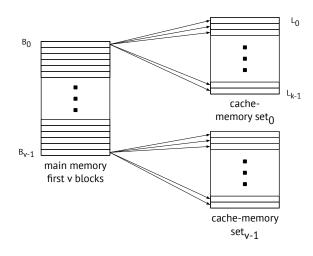

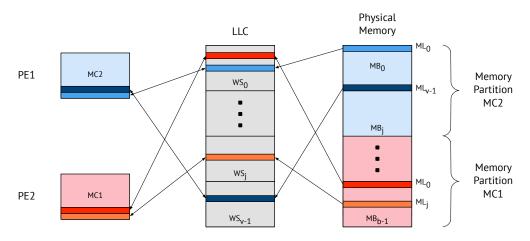

| 4.3  | Shared way-set cache principle                                              |     |

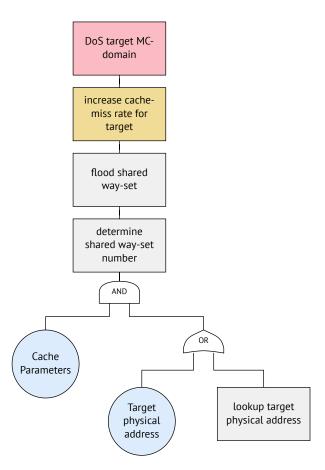

| 4.4  | Cache DoS attack tree                                                       | 105 |

| 4.5  | Target address array allocation principle                                   | 107 |

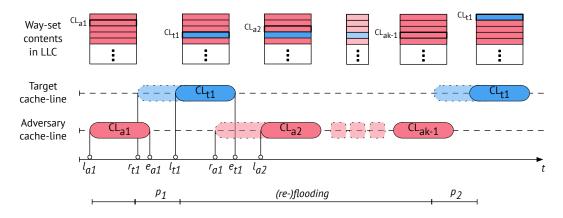

| 4.6  | Timing diagram in flooded way-set                                           | 108 |

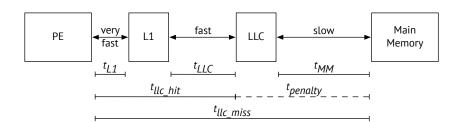

| 4.7  | NUMA and cache memory access latencies                                      | 110 |

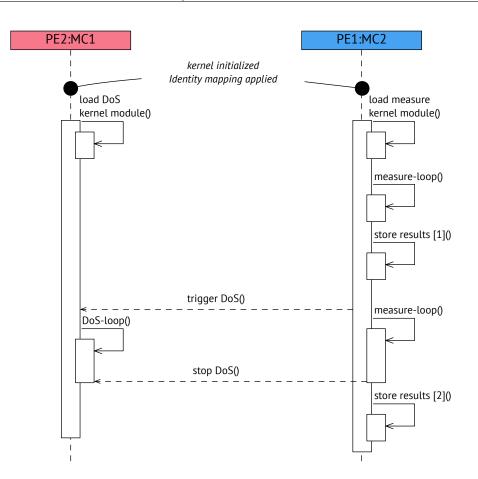

| 4.8  | Sequence diagram of thrashing measurements                                  | 117 |

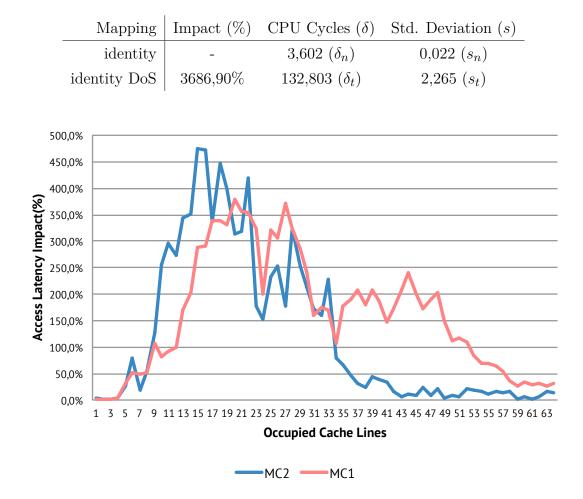

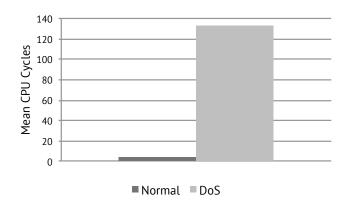

| 4.9  | Comparison of way-set occupancy                                             | 118 |

| 4.10 | Identity memory mapping                                                     | 119 |

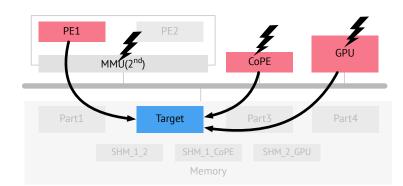

| 4.11 | Breach or circumvent memory protection controls in a SoC                    | 121 |

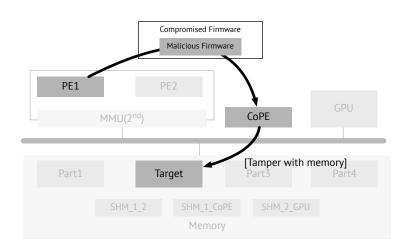

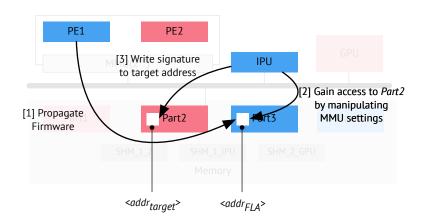

| 4.12 | Misuse scenario utilizing a co-processor to attack a target memory area.    | 122 |

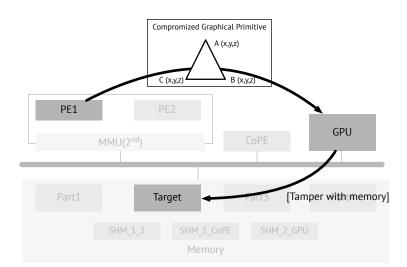

| 4.13 | Misuse scenario utilising a GPU to attack a target memory area              | 123 |

| 4.14 | Implemented attack vector.                                                  | 126 |

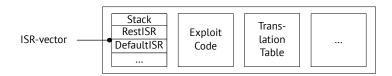

| 4.15 | Memory mapping (extract) for the attack vector.                             | 128 |

| 4.16 | Exploitation firmware structure overview                                    | 129 |

| 4.17 | Exploitation firmware attack sequence.                                      | 130 |

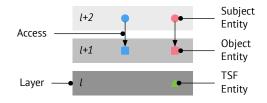

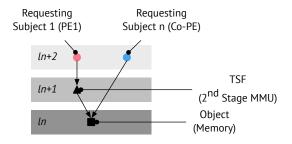

| 4.18 | System layers and entity relationships                                      | 133 |

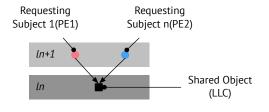

| 4.19 | Generalized access control problem                                          | 134 |

| 4.20 | Resource sharing                                                            | 135 |

| 5.1  | Primary and secondary countermeasures in relation to exploitation and       |     |

|      | asset                                                                       | 148 |

| 5.2  | Distributed access control.                                                 | 151 |

| 5.3  | Modified MPSoC architecture to prevent from direct access misuse. $\ . \ .$ | 152 |

| 5.4  | Object sharing security problem model                                       | 152 |

| 5.5  | MMU utilized as means of access control                                     | 153 |

| 5.6  | Integration of a secondary countermeasure on the intermediate level         | 153 |

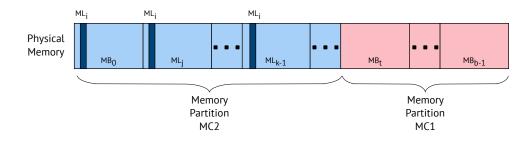

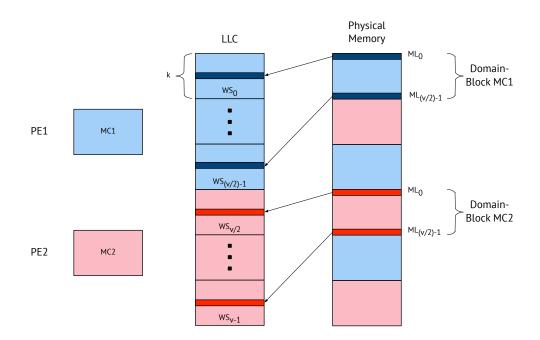

| 5.7  | Principle of domain blocks with exemplary mapping of main memory. $\ .$     | 156 |

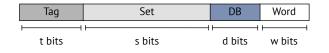

| 5.8  | Addressing of domain-blocks in main memory                                  | 157 |

|      |                                                                             |     |

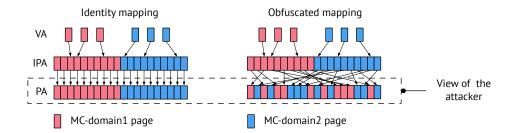

| 5.9  | Principle of randomized memory assignment                               |

|------|-------------------------------------------------------------------------|

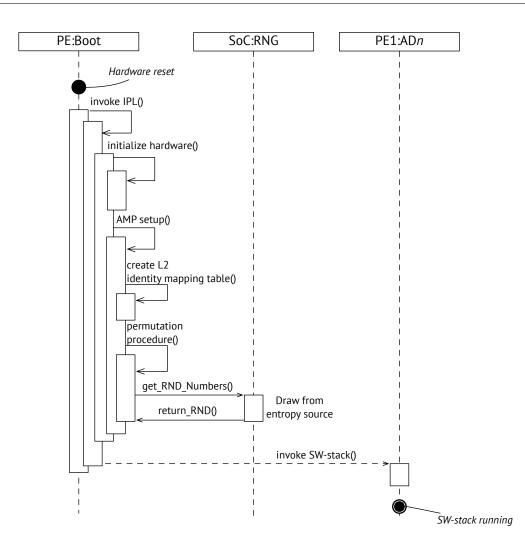

| 5.10 | Integration into the boot process                                       |

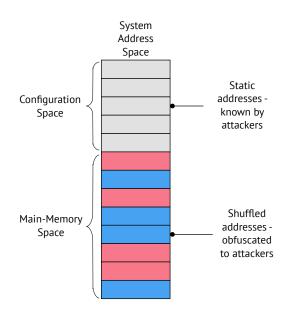

| 5.11 | Coverage of the main memory shuffling                                   |

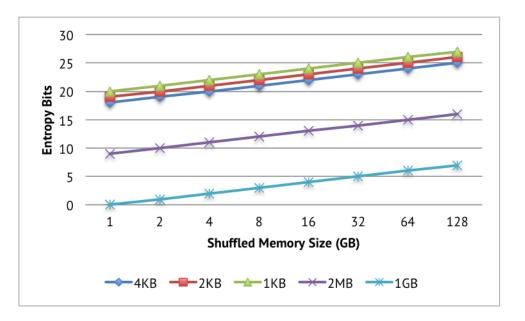

| 5.12 | Comparison of page size, shuffled memory size and the resulting entropy |

|      | bits                                                                    |

| 6.1  | Comparison of identity and DB mapping                                   |

| 6.2  | Memory bandwidth comparison                                             |

| 0.0  |                                                                         |

| 6.3  | DFD of the Type-1 hypervisor system architecture                        |

### List of tables

| 2.1  | Impact severity classes [67]                                              | 38  |

|------|---------------------------------------------------------------------------|-----|

| 2.2  | Attack Potential rating table [173]                                       | 39  |

| 2.3  | Attack Potential level and likelihood [173]                               | 40  |

| 2.4  | Security risk level [67].                                                 | 41  |

| 2.5  | Required and Residual AP (based on [173, p. 418])                         | 42  |

| 2.6  | Microsoft STRIDE Threats. [154]                                           | 42  |

| 2.7  | Data flow diagram                                                         | 43  |

| 2.8  | Threats per Data Flow Diagram (DFD) Element                               | 43  |

| 2.9  | CVSS Base Score [47]                                                      | 46  |

| 2.10 | CVSS Base Score continued [47]                                            | 47  |

| 3.1  | Listing of logical level threats, including a description of the violated |     |

|      | security goals.                                                           | 85  |

| 3.2  | Technical DFD: STRIDE-per-element. Check marks in brackets state          |     |

|      | out-of-scope threats.                                                     | 87  |

| 3.3  | STRIDE-per-element analysis                                               | 89  |

| 3.4  | Impact analysis (Safety, Financial, Operational, Privacy). $\ldots$       | 91  |

| 3.5  | Attack: $PE$ s memory base is tampered with by adjacent $PE$              | 92  |

| 3.6  | Attack: $PE_i$ disrupts $PE_j$ access to $LLC$                            | 93  |

| 3.7  | Risk analysis results.                                                    | 94  |

| 4.1  | Caching terminology and parameters                                        | 103 |

| 4.2  | Symbols for Cache Scheduling                                              | 108 |

| 4.3  | Symbols of cache access latency metrics.                                  | 110 |

| 4.4  | CVSS base score of the cache-thrashing exploit concept                   |

|------|--------------------------------------------------------------------------|

| 4.5  | Measurement symbols                                                      |

| 4.6  | Overview of the measurement results                                      |

| 4.7  | Common Vulnerability Scoring System (CVSS) temporal score of the         |

|      | Last Level Cache (LLC) disruption pentest                                |

| 4.8  | CVSS base score of the access control breach                             |

| 4.9  | CVSS temporal score of the co-processor misuse pentest                   |

| 5.1  | Tactics for threat mitigation (summary of [154, p. 145ff])               |

| 5.2  | Domain-block specific parameters. In addition to Table 4.1 157           |

| 5.3  | Platform cache parameters                                                |

| 5.4  | Entropy and probability symbols                                          |

| 6.1  | CVSS base score of the domain-block concept                              |

| 6.2  | Effectiveness Domain Block concept                                       |

| 6.3  | Measurement symbols                                                      |

| 6.4  | Overview of the measurement results                                      |

| 6.5  | CVSS Environmental score of the Domain-Block mapping 181                 |

| 6.6  | Attack: $PE_i$ disrupts $PE_j$ access to $LLC$ with applied Domain-Block |

|      | mapping                                                                  |

| 6.7  | Domain-Block Mapping: residual risk analysis results                     |

| 6.8  | CVSS base score of the memory-map shuffling concept                      |

| 6.9  | Effectiveness memory-map shuffling countermeasure                        |

| 6.10 | CVSS Environmental score of the Memory-Map Shuffling 186                 |

| 6.11 | Modified Attack Potential: $PE_i$ is tampered with by adjacent $PE$ with |

|      | applied Memory-Map Shuffling                                             |

| 6.12 | Residual risk analysis results                                           |

| 6.13 | Hypothesised attack: $OSguest$ disrupts adjacent $OSguest's$ access to   |

|      | LLC                                                                      |

| 6.14 | Hypothesised attack: OSguest is tampered with by adjacent OSguest. 191   |

## Introduction

1

### Contents

| 1.1 | Motivation of This Research | <b>2</b> |

|-----|-----------------------------|----------|

| 1.2 | Research Goal               | 5        |

| 1.3 | Structure                   | 5        |

### 1.1 Motivation of This Research

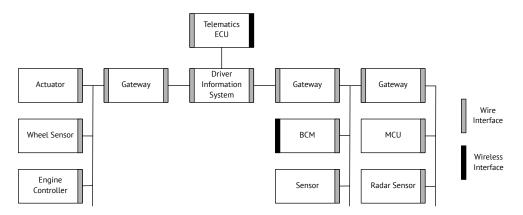

Complex systems such as automobiles consist of a plethora of Electronic Control Unit (ECU)s. The number of such embedded devices ranges from 60 over to 100, depending on the particular model [117]. Traditionally, each of those ECUs were dedicated to a specific purpose, meaning roughly to be categorized into sensors, actuators and processing units. For example, the brake controller actuates on the de-acceleration of the vehicle, while the cluster instrument processes and provides a visualization of the driving information to the driver, as well as, the so-called head unit that processes the infotainment features and provides it to the user. However, the consolidation of functions into a single system platform (such as an ECU) is an emerging trend in automotive system engineering [90]. The vehicle Electric/Electronic (E/E) architecture has changed from many-single purpose ECU networks to a few so-called centralized Domain Control Unit (DCU)s [76, 162]. This might be motivated by the need to efficiently implement driver assistance features such as the Electronic Stabilization Program (ESP) at a centralized point within the vehicle. Furthermore, Advanced Driver Assistant Systems (ADAS) features aiming at the automotive megatrend, automated driving, imply much more fusion and processing of data [34].

The challenge induced by this consolidation is to consider the diverse quality goals of the different functions and features. To refer back to the previous example, there are functions obviously dealing with safety of the driver, such as the brake controller. Accordingly, the reliability of that function is crucial not only to the driver itself but also for many stakeholders. In contrast to that, infotainment features demand processing power in order to embellish the user experience. Consequently, the supply chain for these domain controllers is differently facilitated. In the old-fashioned landscape, each supplier delivered a system consisting of the hardware and software to the customer (Original Equipment Manufacturer (OEM)) who is integrating it into the vehicular network. Considering domain controllers, the hardware is supplied by one party and the software that implements the functions is delivered by third parties. This challenges the trustworthiness of each delivery [19]. As a result, domain controllers are multi-tenant Mixed Criticality Systems (MC-systems). They aim for function consolidation while keeping them separated as they were before in dedicated ECUs.

By introducing the connected-car, automobiles have become the next *thing* in the Internet-of-Things (IoT). An increasing connectivity of the vehicle will transfer automobiles from smart cars to self-driving (autonomous) cars [125]. The possibilities of communication to either, other vehicles (Vehicle-to-Vehicle (V2V)), to the infrastructure

3

(Vehicle-to-Infrastructure (V2I)) or to online (cloud) services are tremendous. Many value-adding online services or a virtual 360-degree view will be made possible. However, along with the increasing connectivity, a number of security incidents are observable. This is particularly caused by the increased attack surface due to the new, remotely accessible interfaces. Researchers began in 2011 to conduct surveys to turn out the attack surfaces of modern automobiles [25, 121]. The wireless entry vectors for adversaries are broad, ranging from near field communication technologies such as Bluetooth over to Long Term Evolution (LTE), wide range, technologies. Recently, it has been demonstrated that those services are exploitable in order to introduce a safety-relevant incident [59, 122, 158]. These grounds finally gave a rise to the need of sophisticated security engineering within the automotive development [137]. Meaning, former assumptions are made invalid. Attack surfaces go extensively far beyond direct physical access to the vehicle [25]. The benefit of bringing rigidly implemented security engineering into the development cycle will help to increase the security of products [176].

Bringing the previous arguments together, there are efforts to consolidate functions into powerful domain controllers inside the vehicle. In parallel, features of the vehicles have lead to new mega trends in mobility. This is not only grounded in connectivity, but to a significant extent driven by it. On the other hand, this also brings stakeholders to the field who wish to misuse those developments for their own purposes. This is why making considerations to security in those areas is necessity.

So, it is reasonable to assume that adversaries have found their way into a single system, such as an ECU in a vehicle. It is then worthwhile to raise the question: how does a compromisation from the outside propagate through the entered system? What steps are necessary for the attacker in order to reach his goal? The goal, in this case, is something they want to gain benefit from. From the protection perspective, the aim is to make it *hard* or *harder* to take a further step into the system. Furthermore, the number of steps to take shall be as high as possible, which is the core idea of defence-in-depth [7]. That means hurdles will be integrated that facilitate such previously mentioned steps. Concepts, such as isolation or separation, address this aim. Those concepts aim for the effort to prevent one entity from interfering with another. As an example, particularly in automotive systems, a function's security properties such as the integrity and availability will need to avoid external adversarial actions, in order to reduce the risk of safety impacts. A practical example of isolation mechanisms are network firewalls that separate network segments from each other.

How those isolation mechanisms are facilitated depends on the system and its technical architecture. From this technical viewpoint, isolation of functions can be achieved on several levels of the system architecture. These levels apply to both the software-stack and the hardware. For example, software levels are often differentiated by privilege levels. Here, processes which represent the actual functions, operating systems which manage the resources for the processes and the hardware, are worth mentioning. If multiple Operating Systems (OSs) are applied, then virtualization comes into play. Meaning, a further layer is added to the system levels. Particularly, virtualization is not new to the automotive embedded systems domain [126]. However, the specific implementation experienced new opportunities due to the integration of virtualization capabilities into the embedded micro-controllers.

Asymmetric Multiprocessing (AMP) is a way to approach isolation by utilizing dedicated hardware capabilities. This enables the separation of several software-stacks, such as OS, on top of it. In contrast to traditional virtualization schemes, whose involve a virtual machine monitor or a hypervisor, the AMP approach lacks this kind of software instance between the multiple OS and hardware [30]. The means of indirection, which is enforcing the isolation, are distributed into the hardware elements. AMP aims at separating resources on the intermediate level between the software-stacks and the hardware elements. As a result, the levels above have an asymmetric access to the hardware resources [108, 109]. By applying the concept of AMP in embedded systems, it experiences a revitalization from the earlier years of large-scale main-frame systems when the OS capabilities of handling several processors on a single hardware were limited. In the field of software engineering, particularly in the automotive area, there are advantages of applying this concept. For example, OS running on top of the AMP system does not need to be modified to run on a hypervisor. Accordingly, the development cost is reduced and the maintenance effort is limited. A further, very substantial aspect in embedded systems is the performance, in this case, more precisely, the negative performance impact by introducing a further level of indirection. AMP systems run the software-stacks directly on the hardware, rather than implement the indirection in software that has, in turn, to be handled by the processor instead of doing other computations [63, 82, 131].

Embedded system hardware is often facilitated by the concept of MPSoCs. This is particularly true for automotive ECUs. MPSoCs combine processors, peripherals and memory through a particular infrastructure to a heterogeneously integrated circuit [75]. As it was mentioned previously, the isolation of software-stacks in AMP systems is moved to the hardware. Since MPSoCs can be seen as a network of hardware elements, the challenge in isolation is to handle this complexity and apply the protection to these elements.

Isolation instantiates aspects that contribute to the security of systems, in this case, of AMP systems. To come up with means to implement protection for isolation is subject to structured security-enabled development processes. However, the continuous character of security has to be taken into account. Assuming there is any inconsistency or vulnerability in the design of isolation, the question arises as to how to handle the immutability of the hardware protection architecture. Despite that the hardware manufacturer might come up with new architecture to fix the weakness, if the system is already deployed, changes to the hardware are impossible or at least very cost intensive. As a result, if the protection mechanisms are moved to the hardware, there is no further line of defence in the case of compromisation. The consequences could be cumbersome, depending on the particular use-case of the system. In order to solve this issue, several strategies are possible. One option is to put an effort into hardening another hurdle at a higher level in order to increase its effectiveness and keep the adversary out of the system. This means the problem is solved at a different place in the environment. If the development is still in progress, one might put an effort into hardening the AMP isolation as it is. For example, this could be done through rigid and formalized development, meaning, it is tried harder to avoid any vulnerabilities.

Nonetheless, the specific issues of AMP system security could also be investigated. This is then applicable to countermeasures that use the AMP specific construction paradigm again to limit the potential of the system of being attacked.

#### **1.2** Research Goal

New paradigms of building systems might require rethinking assumptions made from traditional paradigms. This work seeks to build security patterns for AMP system paradigms. The security pattern shall describe<sup>1</sup> recurring security problems in a particular context and conclude with a security solution. The given concepts shall suitably comply with constraints given by the automotive context.

#### **1.3** Structure

The structure of this thesis is outlined as follows.

<sup>&</sup>lt;sup>1</sup>according to Schumacher et al. [149]

**Fundamental Concepts:** In Chapter 2, the foundations and state-of-the-art information according to the research area is given. It profiles the Target of Evaluation (ToE) and differentiates other, recently applied paradigms. Furthermore, the means of security engineering are elaborated. This concludes with a description of the security process employed in this work. On this basis, the research methodology is described. This includes the research questions, approaches, methods and artefacts conducted throughout this work.

**Risk Assessment: Driver Information System Case Study:** In Chapter 3, the foundations are turned into a case-study showing the application of the previously introduced concepts. Here, a driver information system instantiates an MC-system based on the AMP paradigm. The case-study is intended to provide a context and running example in the thesis. Furthermore, the experimental platform that has been used for several activities throughout this work is explained. The security assessment derives two hypothesised attacks that are investigated further in this document.

**Vulnerability Assessment:** Chapter 4 conducts the vulnerability assessment. Here, the specific security aspects of the hypothesised attacks from the case-study are assessed. Furthermore, the findings are abstracted to a general attack model for the given ToE class.

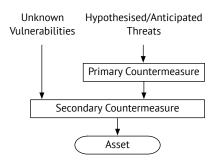

**Risk Treatment:** Measures against the identified findings from the previous chapter are described in Chapter 5. Two countermeasures that address the security issues from the vulnerability assessment are examined. The findings are derived from a general protection model that categorizes the dependencies between the attacks and countermeasures.

Security Evaluation: The security evaluation is conducted in Chapter 6. The attacks and countermeasures have been scored against a common scheme. In this chapter, the effectiveness based on the common scoring scheme is elaborated upon. Furthermore, a brief comparison to a hypervisor based system is given. Here, the findings also are discussed by evaluating the solutions in the context of the case-study.

**Related Work:** In Chapter 7, the findings are aligned with related work in the particular research fields this work deals with.

**Conclusion:** This document concludes with Chapter 8, where a summary of the key contributions and findings of this research is presented. Furthermore, an outline of future work is given.

## **Fundamental Concepts**

2

## Target of Evaluation, Security Process and Research Methodology

#### Contents

| 2.1 Prof | file of Asymmetric Multiprocessing Systems 10 |  |

|----------|-----------------------------------------------|--|

| 2.1.1    | Definitions and Terminology                   |  |

| 2.1.2    | ToE Description                               |  |

| 2.1.3    | Hardware Elements                             |  |

| 2.1.4    | ToE MPSoC Components                          |  |

| 2.1.5    | Security Problem Definition                   |  |

| 2.1.6    | Security Objectives                           |  |

| 2.2 Secu | urity Engineering 31                          |  |

| 2.2.1    | Introduction to Security Engineering          |  |

| 2.2.2    | Security Assessment Methodology 49            |  |

| 2.3 Res  | earch Methodology 54                          |  |

| 2.4 Sum  | mary                                          |  |

Out of the crooked timber of humanity, no straight thing was ever made

#### Immanuel Kant

Discussing the security of a system requires a comprehensive definition of the ToE. Particularly, AMP systems rely on the hardware architecture and composition of hardware elements. This diversity needs to be abstracted in order to handle the complexity on the one hand and make results transferable on the other. In addition, the term *security* is overused in many contexts. It is mandatory to discuss what it means for the intended purpose of this work.

Accordingly, this chapter addresses these two significant issues. It first profiles AMP systems, which facilitates the ToE considered by this work. This definition of how the AMP paradigm is treated is supported by the reflection of the state-of-the-art and differentiation to other system paradigms. The second part provides an overview of how to address security in systems engineering, and concludes with the security assessment methodology applied in this work. Given that foundation, the chapter ends with the description of the research methodology including the research questions, methods and artefacts.

### 2.1 Profile of Asymmetric Multiprocessing Systems

#### 2.1.1 Definitions and Terminology

Asset: Anything that has value to an owner.

**Threat:** Potential cause of an unwanted incident, which may result in harm to a system or organization [86].

Threat Agent / Attacker: Individual who acts adversely on an asset.

Attack: Attempt to destroy, expose, alter, disable, steal or gain unauthorized access to or make unauthorized [86]. use of an asset.

**Risk:** Effect of uncertainty on objectives [86]. Quantitative estimation of an event (attack), with respect to its impact and likelihood to occur.

**Impact:** Negative effect which a successful attack causes.

Attack Potential: The Attack Potential (AP) quantifies the *"effort required to create the attack"* [173, p. 420].

**Risk Treatment:** Process to modify risk [86].

**Risk Mitigation:** A mean which reduces the attack potential and, therefore, the risk of an asset.

Countermeasure: The implementation of a risk mitigation.

**Security function:** Synonym to countermeasure. Implements measure against adversarial actions.

**Vulnerability:** Weakness of an asset or control that can be exploited by one or more threats [86].

**High Level Security Goals:** Confidentiality Integrity Availability (CIA) are the most common and fundamental security goals. Additionally, authenticity and authority are properties a common embedded system setup has to deal with.

The action of acting adversely on a target is referred to as attacking or compromising. The term attack defines a series of actions that achieve a particular objective. The victim of an attacker is referred to as the attack target. In a multi-level system architecture, this includes processes, threads, operating systems, Asynchronous Domains (ADs), etc. For example, an attacker may act adversely on a target AD or a target process, respectively. Reaching the phase of a successful attack, the target's state is considered as being compromised, illicit or malformed. Accordingly, the target's state is considered as being untrusted which is in contrast to the trusted state from before. An attack is usually mounted from a malformed origin, a compromised source or an illicit entity.

#### **Definition and Operational Usage**

The consideration of this work aims for the particular instantiation of separation in an AMP system. AMP describes the paradigm to enforce a spacial distribution of software functions on a common computing platform. Within this work, AMP is referred to  $as^{1}$ :

**Definition 2.1** AMP is a system utilization paradigm aiming for a spacial separation of hardware elements in order to establish ADs on the software layer.

As a result, an AMP system consists of two or more ADs. To address the logical composition of several hardware elements and software components, the term AD is defined.

<sup>&</sup>lt;sup>1</sup>System separation paradigms are elaborated in detail in Section 2.1.2

**Definition 2.2** An AD is a logical composition of software components ran by the same processing element (Central Processing Unit (CPU) core). AD are decoupled from adjacent domains by definition.

Typical uses of an AMP-system are highly integrated systems that aim to combine diverse functions in heterogeneous software-stacks. Accordingly, AMP is a paradigm to organise computer systems such as embedded, desktop and server systems. The intention of facilitating an AMP system has changed over the last decades of computer history. In the early days of mainframes, AMP was used as a stopgap, due to the inability to manage multiple processors within a single operating system. Today's definitions of AMP systems comply to the heterogeneous nature of MPSoCs. Colin [30] defines AMP as a system consisting of multiple processors, each of which can apply a different architecture. Each processor operates on its memory space, while an operating system is not mandatory. Furthermore, communication facilities between the processors are applied. A more technical view on the AMP-paradigm is given by ARM in the technical documentation:

"An Asymmetric Multi-processing (AMP) system enables you to statically assign individual roles to a core within a cluster so that, in effect, you have separate cores, each performing separate jobs within each cluster. This is known as a function-distribution software architecture and typically means that you have a separate OS running on the individual cores. The system can appear to you as a single-core system with dedicated accelerators for certain critical system services." [109, p. 14-7]

In Chapter 3, the concept is applied to an exemplary automotive embedded system.

#### ToE Type

The ToE facilitates the software configuration of a hardware platform. Throughout this work, this facilitation is referred to as the *intermediate layer* between the physical hardware and the logical software-stack(s). As a result, it is considered how the hardware is to be interfaced. There is a direct dependency on the composition of logical software-stacks (ADs) and the composition of hardware elements. In the following sections, the building blocks that are considered in this work are elaborated upon. The hardware platform consists of integrated building blocks. In this work, MPSoCs for embedded environments are considered. Generally, these components include processors and peripherals, for example. The MPSoC elements are considered to be shared by

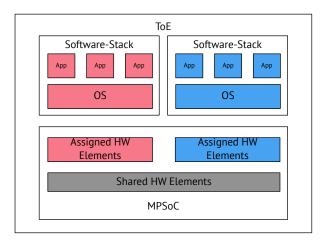

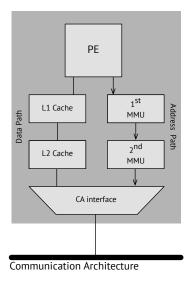

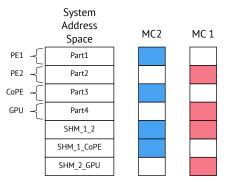

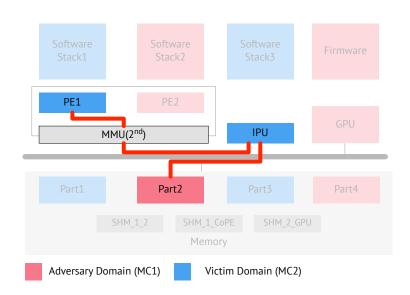

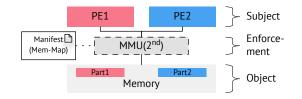

Fig. 2.1 ToE overview.

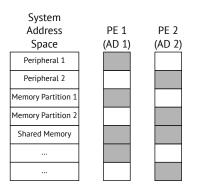

all ADs (referred to as *Shared HW Elements*) or they are assigned to a specific AD (referred to as *Assigned HW Elements*). Figure 2.1 shows a brief overview of the ToE architecture. The figure shows two ADs coring the assigned software-stacks and assigned HW elements in *red* or *blue*, respectively.

#### Non-TOE Software Applications and Functionality

In this work, particular features and functionalities that are run by the described ToE are not considered. This enables a context-free conduction of results. Furthermore, as it is mentioned in the previous section, only the interface between the hardware and the software is concerned. Particular OSes or applications that are run by such an AMP-based ToE are out-of-scope. For example, it will not matter if the OS implements a microkernel or monolithic-kernel architecture.

#### 2.1.2 ToE Description

#### Architecture

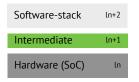

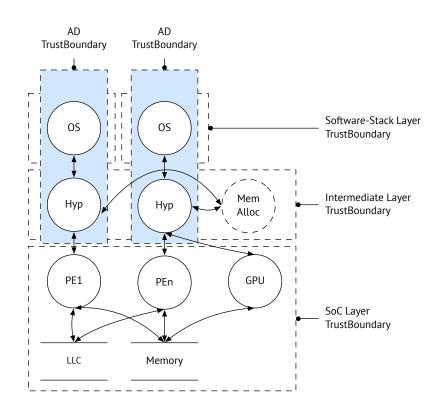

**System Privilege Hierarchy** The ToE consists of several logical ADs that are a collection of software-stacks and physical hardware elements. In general, the considered ToE architecture is comprised of two main layers: the *software-stack* and the *SoC Layer*. It is considered that the hardware allows to run software in the software-stack in more than one privilege levels. This is needed to allow, privileged software to separate less privileged software components from each other. In order to implement an AMP system, MPSoC elements need to be assigned to a particular AD. Accordingly, the

Fig. 2.2 Layered system hierarchy.

layer that separates the several MPSoC elements and assigns them to software-stacks must run on a higher privilege level than the software-stack. As a result, this is referred to be run on the *intermediate layer*. A visualization of the layers is depicted in Figure 2.2.

Layering in general aims at maintaining the divide-and-conquer principle to handle complex systems. Therefore, in the following, the platform layer structure of a system platform is given. Architectural layers aiming at dividing complex systems horizontally. This makes it possible to distinguish specific aspects within several layers from each other. Particularly, in security assurance methodologies a layered consideration is recommended. A prominent example is the Common Criteria (CC) security evaluation framework [172]. To conclude, layering will provide the foundation for the security consideration within this work. In the following, the particular layers are introduced.

SoC layer: The System-on-Chip (SoC) layer is considered to instantiate hardware layer. Typical entities are the distinct building blocks of that a SoC consists of. These building blocks are commonly referred to as Intellectual Property (IP) blocks, or cores. IP blocks are, by their nature, pre-qualified and integrated into the SoC layout. A minimal set of IP blocks includes a Processing Unit (PU), Read Only Memory (ROM), and Random Access Memory (RAM). MPSoCs integrate more than one PU. The communication is facilitated by simple protocols such as Serial Peripheral Interface (SPI) [106] or  $I^2C$  [106, 151] or complex communication infrastructures such as the ARM Advanced Microcontroller Bus Architecture (AMBA) and Advanced eXtensible Interface (AXI) bus [11]. The IP blocks are considered to be configurable via a management interface. Technically, this is represented by memory registers mapped to the system memory address space. This is elaborated upon in the following sections on the practical implications of AMP systems. Furthermore, a security-relevant configuration can be applied, such as access control to the IP blocks.

**Intermediate layer:** The intermediate layer represents the link between the hardware layer and the software layer. Entities on this layer are distinct software

stacks. For example, these include operating systems (OS) of any kind or more straightforward constructs such as firmware. To create these entities, the configuration interface of the SoC layer has to be utilised. Typical configuration interfaces include: translation tables for the Memory Management Unit (MMU)s to apply access control and proper function of the memory accesses, interrupt tables to facilitate signalling between the PU and power control for energy and frequencies to configure the appropriate clocks for the hardware elements. The intermediate layer is sometimes referred to as hypervisor layer or the layer at which the Virtual Machine Monitor (VMM) is implemented.

Software-Stack layer: On the software-stack layer, everything is included that runs on top of the hardware elements. Typically, this includes an OS representing the lowest logical layer of the software stack. Entities on this layer are typically the infrastructure to manage the operation of applications. Usually, this infrastructure is referred to as the OS kernel. In general, two types of kernels are differentiated: micro-kernels where the infrastructure runs as much as possible in small and self-contained components and monolithic kernels that integrate the entire functionality into a common, so-called, kernel-space. To fulfil extensive requirements of safety-relevant or multimedia applications, different types of operating systems are used. These inlcude, Real-time Operating System (RTOS), General Purpose Operating System (GPOS) or Mobile Operating System (mobileOS). On top of the OS, the functional logic of the system is encompassed. Features and applications of the system are implemented at this logical application layer. Technically, the layer entities are represented as processes or threads that are maintained by the OS. For example, Linux OS consists of the OS layer and the application layer. The latter is called user-space and the former kernelspace. Despite the separation of user-space and kernel-space privilege granularity, processes can be assigned to access control compartments with fine-grained privileges.

**Differentiation of Separation Paradigms** This section seeks to differentiate the AMP-idea from other paradigms to partition software-intense systems. Partitioning, or separation, is achievable on all layers of a system architecture. An important aspect is the utilization and management of the hardware. This influences at which layer the special separation must be implemented.

Symmetric Multi Processing. Symmetric Multi Processing (SMP) systems are the pendant to AMP systems. Here, only one software-stack instance is controlling the hardware, symmetrically. SMP systems apply multiple processors as well, but they all operate in the same memory space. Typically, a single instance OS is used to run the sharing all processors [30]. The vast majority of computer systems utilize the SMP paradigm. The infrastructure of a single OS is managing the underlying resources and makes them available for applications to the upper system levels.

"[...] SMP is a software architecture that dynamically determines the roles of individual cores. Each core in the cluster has the same view of memory and shared hardware. Any application, process, or task can run on any core, and the operating system scheduler can dynamically migrate tasks between cores to achieve optimal system load. A multi-threaded application can run on several cores at once." [109, p. 14-3]

**Virtualization** Virtualization, in general, is a term vastly used in the IT and desktop computing area. Silberschatz et al. defines virtualized systems as follows.

"Generally, with a virtual machine, guest operating systems and applications run in an environment that appears to them to be native hardware and that behaves toward them as native hardware would but that also protects, manages, and limits them." [155, p. 711]

The main purpose is to run multiple operating systems on a single system. In literature, a virtual machine monitor (VMM) or hypervisor facilitate the infrastructure to create virtual machines.

"A relatively small control program called Virtual Machine Monitor (VMM) or Hypervisor is placed between the OS and the hardware. Typically the VMM executes in privileged mode and can host one or more operating systems – GuestOSs – in a sandbox called Virtual Machine: a controlled construct of the underlying hardware." [120, p. 2]

As a result, virtualization endeavours to put a privileged instance underneath guest OSs in order to manage their access to the underlying hardware. These instances are commonly referred to as hypervisor or VMM. The community differentiates three types of facilitating virtualization [155].

**Type-0:** The virtualization capabilities are incorporated into the hardware. The virtualization infrastructure is managed by a configuration interface.

**Type-1:** A *type-1* virtualization runs the hypervisor bare-metal on hardware.

**Type-2:** A *type-2* solution relies on a so-called host OS that manages the system abstraction. The host OS provides the infrastructure to virtualize the guest OS.

Furthermore, it is differentiated between para-virtualized systems and full-virtualized systems. The former considers adaptions of the guest OSs to the underlying virtualization solution in order to make it functional or to improve performance. The latter aims to fully abstract the hardware by the hypervisor.

**Type-0 Virtualization and AMP** In this work, Type-0 virtualization capabilities of the hardware are treated as a precondition in order to implement an AMP system. AMP describes the aim of dividing hardware elements into ADs. Therefore, the hardware, or the particular elements of the hardware, must support assignments to logical compositions. The practical implications and the interface of recent hardware architectures are elaborated in Section 2.1.3.

"Implementing efficient virtualized systems cost effectively requires hardware support. In particular memory management can provide great challenges and have severe repercussions on system reliability and performance. To address this ARM is introducing the Virtualization Extensions to its ARM v7 architecture and the System Memory Management Unit (SMMU) Architecture." [120, p. 1]

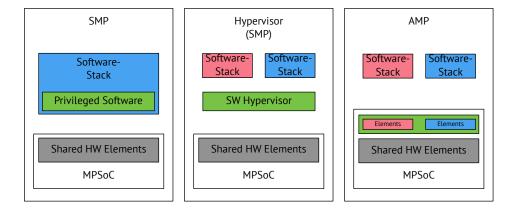

**Comparison of Domain Separation Paradigms** Vertical separation softwarestacks is a well-established technique to organise software entities in a software-stack. In the following, it is briefly shown how AMP relates to other partitioning schemes. In general, three schemes are differentiated. Figure 2.3 depicts three paradigms. The architectural system layers are visualized according to the multilayer scheme shown in Figure 2.2. The separated logical domains are coloured in *blue* or *red*, respectively. On the left, the SMP concept is depicted. It shows one *domain* that spans over the entire *software-stack* as well as the entire *hardware*. Accordingly, the software-stack controls the entire hardware symmetrically by privileged software that is included into the software-stack. In contrast to that, in the right example, AMP is depicted. Here, two domains span over dedicated *software-stacks* and assigned hardware *elements* of the MPSoC. These elements are considered as residing on the intermediate layer. In the centre, domain separation using a hypervisor on the intermediate layer is shown. Here, the *hypervisor* abstracts the underlying hardware and provides a context for the software-stacks on top of it. In this way, two separated domains are created.

In Figure 2.3, the three approaches to create software partitions are shown.

Fig. 2.3 Comparison of domain separation paradigms.

# 2.1.3 Hardware Elements

MPSoC fit well into the heterogeneous environment such as the automotive. Accordingly, Wolf et al. defines MPSoCs as follows:

"Multiprocessor systems-on-chips have emerged in the past decade as an important class of very large scale integration (VLSI) systems. An MPSoC is a system-on-chip—a VLSI system that incorporates most or all the components necessary for an application—that uses multiple programmable processors as system components. ... They are not simply traditional multiprocessors shrunk to a single chip but have been designed to fulfill the unique requirements of embedded applications." [186, p. 1701]

Basically, two general types of MPSoCs are differentiated in literature: heterogeneous and homogeneous architectures [75]. The former is composed of diverse system components such as processors, memories, accelerators and peripherals. The latter refers to the multiple instantiation of the identical processor system component [179]. In many cases, the heterogeneous approach fits well with automotive needs. In this case, heterogeneous means that a combination of different processor architectures can be possible. Accordingly, plenty degrees of freedom regarding the composition of functions are possible. For example, a low energy, real-time capable architecture can be combined with a high-performance general-purpose processor. Furthermore, the integration of pre-qualified software can easily be migrated to the platform by adding the suitable processor architecture to the MPSoC. To this end, the high-level integration demands are supported by the hardware platform as well.

Wolf et al. analysed in [186] the technological history of MPSoC and states that the most MPSoC architectures follow a heterogeneous structural taxonomy. The authors argue that the architectural design is mostly influenced by the application of the hardware. Nevertheless, standards can influence the MPSoC structure as well as the centralization of a particular system component. In such cases, often a communication architecture centralised approach is realised [186].

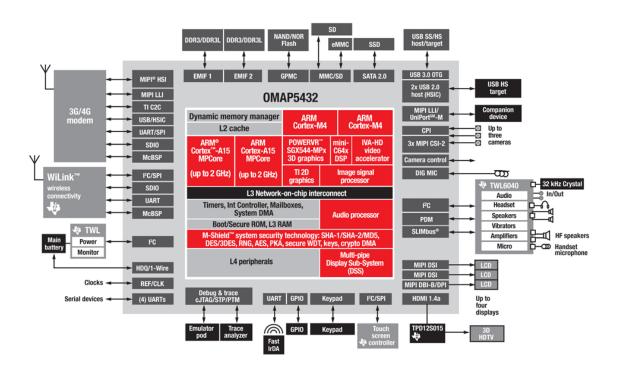

Many SoC vendors establish platform-based approaches to foster their product-lines. Usually, the platforms are tailored to a specific application area, such as in-vehicle infotainment systems, including a certain amount of variability to fit the product to the customer's needs. The variations reach from adding more processor cores, more memory or different accelerators such as Digital Stream Processor (DSP) or Graphical Processing Unit (GPU)s. As a result, the SoCs emerge from very specialized to commodity platforms based on reusable components [22].

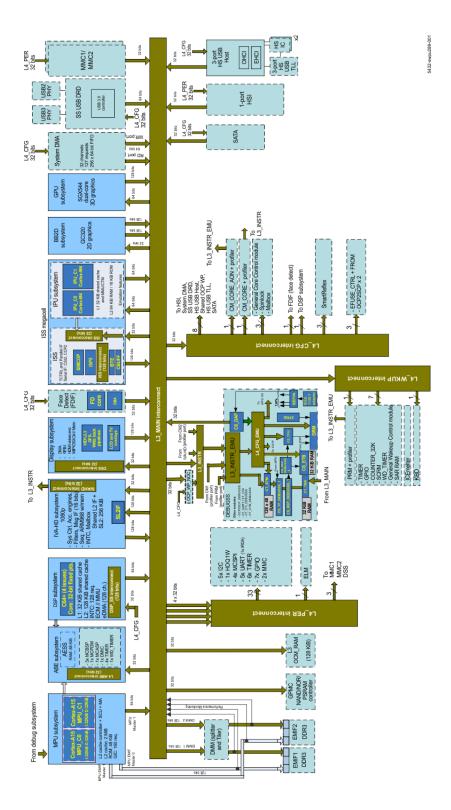

Practical, state-of-the-art and automotive relevant examples include the MPSoC platforms such as Texas Instruments OMAP, Freescale iMX.X, Xillinx  $Zync^2$  and Renesas  $RCar^3$ .

# 2.1.4 ToE MPSoC Components

The ToE consists of a particular set of typical MPSoC components that are presented in this section. In general, this work considers MPSoCs as follows:

"They combine several embedded processors, memories and specialised circuitry (accelerators, I/Os) interconnected through a dedicated infrastructure to provide a complete integrated system. Contrary to SoC s, MPSoCs include two or more master processors managing the application process, achieving higher performances." [75, p. 1]

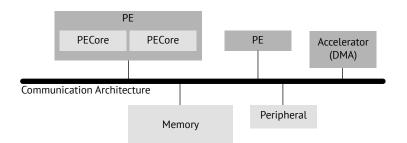

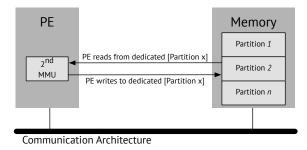

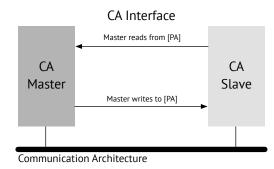

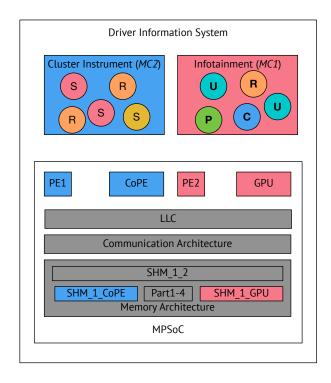

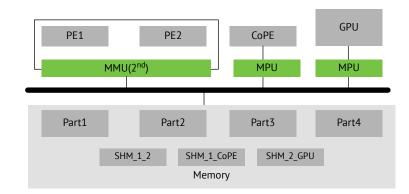

Accordingly, MPSoCs facilitated by the ToE integrate diverse system elements such as Processing Element (PE), Memory Architecture (MA), Communication Architecture (CA) and further peripherals. Particularly, heterogeneous MPSoCs integrate diverse PEs each of which is intended for different purposes. Sometimes these heterogeneous processor integrations are also referred to as multi-core or many-core SoC. Viewing

<sup>&</sup>lt;sup>2</sup>http://www.xilinx.com/products/silicon-devices/soc.html

<sup>&</sup>lt;sup>3</sup>http://am.renesas.com/applications/automotive/cis/cis\_highend/index.jsp

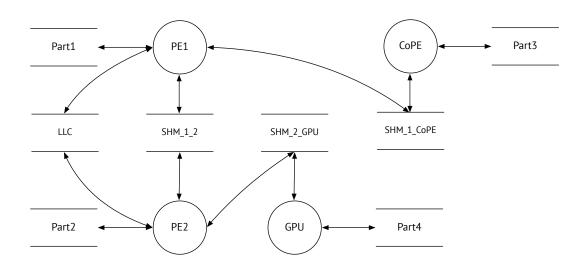

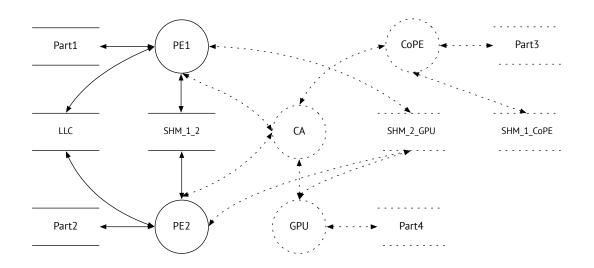

Fig. 2.4 Considered MPSoC components.

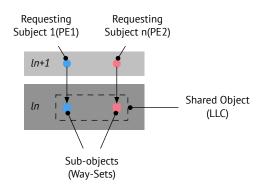

from the perspective of *Flynn's Taxonomy*, the general architecture is based on the Multiple Instructions Multiple Data (MIMD) architecture [167]. Multiple processors work independently and asynchronously on different data sets while sharing a common hardware platform. In Figure 2.4 an overview over the considered SoC elements is depicted. These elements are described in detail in the following sections.

## **Processing Elements**

The term PE will be used as a general-purpose abstraction for active system elements or IP-cores. Active means, in this context, that the PEs have their independent and asynchronous control flow. Usually, this control flow is defined by machine code that the processor is operating on. CPU is a typical example of a PE. Nevertheless, the PEs does not necessarily need to impersonate a processor in a general meaning. Co-processors, accelerators such as GPUs or DSPs which usually support the PE by special purpose computing results. The heterogeneous nature of MPSoCs allows for the combination of different processor architectures. Those include Reduced Intruction Set Computer (RISC) architectures, stream processors (such as GPU), DSP and Field Programmable Gate Array (FPGA). A widely used representative is the ARM architecture. Nevertheless, real-time affine architectures such as the SH-4 or PowerPC can be included as well. As an example, the Renesas R-Car H3 platform provides a SH-4 system component within their automotive infotainment portfolio.

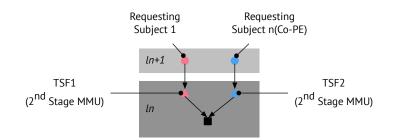

The internal components of the PE depend on their specific architecture. Most commonly, they integrate a processor core and infrastructure to handle data/instructions and addresses. Particularly, the MMU plays an important role in redirecting address requests from PUs<sup>4</sup>. In Figure 2.5, a two-stage address translation is depicted. Furthermore, the processor caches represent a key element of a PE. Particularly from the performance perspective, characteristics such as size, organisation and relationship

$<sup>^{4}</sup>$ The MMU will be elaborated in more detail in Section 2.1.4

Fig. 2.5 Generalized MPSoCstructure combining diverse elements.

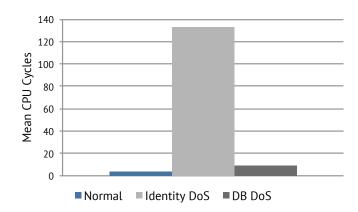

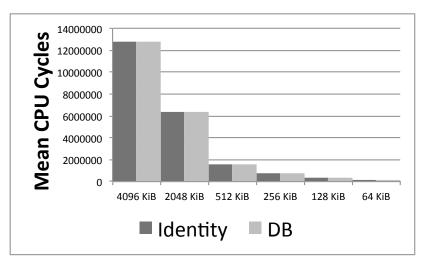

to the cached memory are key factors. Modern PEs operate on a two-levelled cache subsystem. Level one is typically small in size and usually is split into an instruction cache and data cache (I-cache and D-cache), while for the second level, the instructions and data are mixed and the cache size is significantly larger. At the end of the line, the PE is connected by an interfacing element which enables the access to the communication architecture. This concept is depicted in Figure 2.5.